### PEOPLE'S DEMOCRATIC REPUBLIC OF ALGERIA Ministry of Higher Education and Scientific Research

### University Hadj Lakhdar -BATNA 1-

Faculty of Matter Sciences Department of Physics

A DISSERTATION

### Presented in fulfillment of the requirement of the degree of

**Doctorate of Sciences**

By:

**TOUFIK BENTRCIA**

Entitled:

## Study and modeling of multigate nanoscale MOSFETs including quantum and traps effects: Application to the nanoscale devices design

Specialty: PHYSICS OF METAL MATERIALS AND SEMICONDUCTORS

Defended in 21/04/2019

Approved by:

### Committee members:

| President: | Dr. Mohamed CHAHDI       | Professor | University of Batna 1            |

|------------|--------------------------|-----------|----------------------------------|

| Advisor:   | Dr. Fayçal DJEFFAL       | Professor | University of Batna 2            |

| Members:   | Dr. El-djemaï BELBACHA   | Professor | University of Batna 1            |

|            | Dr. Abdelhamid BENHAYA   | Professor | University of Batna 2            |

|            | Dr. Abdelouahab BENTABET | Professor | University of Bordj Bou-Arréridj |

|            | Dr. Ramdane MAHAMDI      | Professor | University of Batna 2            |

RÉPUBLIQUE ALGÉRIENNE DÉMOCRATIQUE ET POPULAIRE Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

### Université Hadj Lakhdar - BATNA 1-

Faculté des Sciences de la Matière Département de Physique

THÈSE Présentée en vue de l'obtention du

Diplôme de Doctorat

Par:

TOUFIK BENTRCIA

Thème:

# Étude et modélisation des MOSFETs nanométriques à multi-grille incluant les effets quantiques et de pièges: Application à la conception des composants nanométriques

Spécialité: PHYSIQUE DES MATÉRIAUX MÉTALLIQUES ET SEMICONDUCTEURS

Soutenue le 21/04/2019

### Devant le jury:

| Président:    | Dr. Mohamed CHAHDI       | Professeur | Université de Batna 1            |

|---------------|--------------------------|------------|----------------------------------|

| Rapporteur:   | Dr. Fayçal DJEFFAL       | Professeur | Université de Batna 2            |

| Examinateurs: | Dr. El-djemaï BELBACHA   | Professeur | Université de Batna 1            |

|               | Dr. Abdelhamid BENHAYA   | Professeur | Université de Batna 2            |

|               | Dr. Abdelouahab BENTABET | Professeur | Université de Bordj Bou-Arréridj |

|               | Dr. Ramdane MAHAMDI      | Professeur | Université de Batna 2            |

### **Acknowledgments**

Chis research work has been conducted within the LEPCM laboratory at the University of Batna -1-.

First of all, I would like to capture this opportunity to express the best gratitude to my advisor Professor Fayçal Djeffal. Che current research outcome could not be reached without his deepest expertise and continuous guidance all along the past years. Sincerely, I would like to thank him a lot for the balance between rigor, intelligence and humor, which has made our lab an amazing research environment. His inspirations and pertinent orientations have always allowed shedding light and tackling encountered problems.

I would like to thank Professor Mohamed Chahdi from the University of Batna -1- for taking the heavy responsibility of presiding the examination committee despite his many duties. My thanks go also to the examination committee members namely Professor Eldjemi Belbacha. from the University of Batna -1-, Professor Abdelhamid. Benhaya from the University of Batna -2-, Professor Abdelouahab Bentabet from the University of Bordj Bou-Arréridj and Professor Ramdane Mahamdi from the University of Batna -2-, for taking valuable time to review my dissertation and provide relevant comments regarding my research work.

I appreciate the support of my friends during all stages of this dissertation through sound discussions and shared joyful moments. I apologize for not mentioning any noun but I am sure that genuine friends know they are concerned.

Finally, I want to express sincere gratitude to all my family and especially my parents, for whom I hide billions of sentences carved in my heart not necessary to be written.

### **Dedication**

Co all whom I love, I dedicate this modest work.

# List of contents

| Li | st of                  | contents                                                                         | xi       |  |

|----|------------------------|----------------------------------------------------------------------------------|----------|--|

| Li | st of                  | figures                                                                          | xiii     |  |

| Li | List of tables xvii    |                                                                                  |          |  |

| Li | List of algorithms xix |                                                                                  |          |  |

| Ge | enera                  | d introduction                                                                   | 1        |  |

| 1  |                        | rview of MOSFET devices : Evolution, properties and modeling                     | 7        |  |

|    | 1.1                    | Introduction                                                                     | 9        |  |

|    | 1.2                    | Historical evolution of CMOS technology                                          | 9        |  |

|    | 1.3                    | Paradigm of MOSFET devices                                                       | 13       |  |

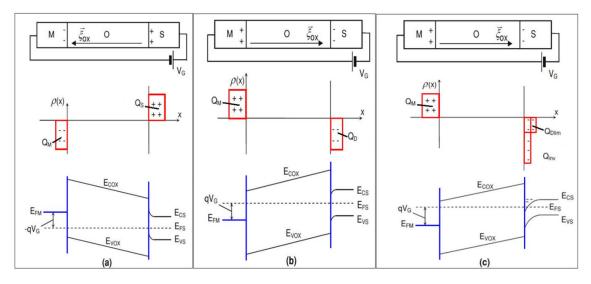

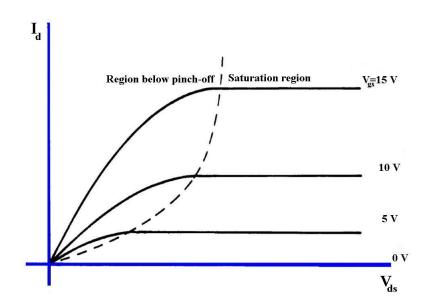

|    |                        | 1.3.1 Description and operation regimes of the standard MOSFET structure         | 13       |  |

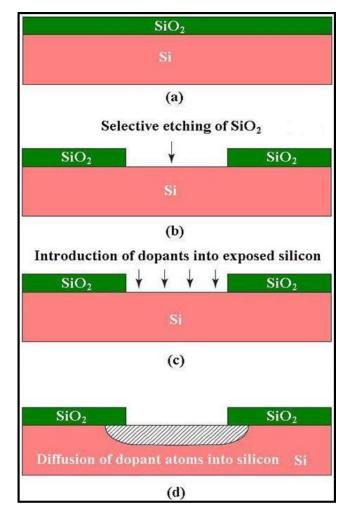

|    | 14                     | 1.3.2 Fabrication process of MOSFET devices      MOSEET performance manufactures | 16<br>20 |  |

|    | 1.4                    | MOSFET performance measures1.4.1Subthreshold parameters                          | 20<br>20 |  |

|    |                        | 1.4.1       Subtrieshold parameters         1.4.2       Small signal parameters  | 20<br>22 |  |

|    |                        | 1.4.2       Sinan signal parameters         1.4.3       Linearity parameters     | 23       |  |

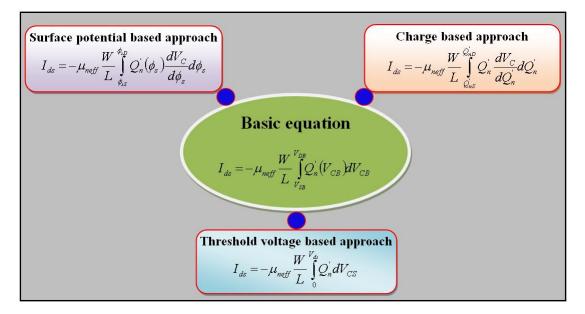

|    | 1.5                    | Various approaches of MOSFET modeling                                            | 24       |  |

|    | 1.0                    | 1.5.1 Threshold voltage based models                                             | 24       |  |

|    |                        | 1.5.2 Charge based models                                                        | 25       |  |

|    |                        | 1.5.3 Surface potential based models                                             | 25       |  |

|    | 1.6                    | Downscaling of MOSFET devices and degradation effects                            | 26       |  |

|    | 1.7                    | Emergent techniques for enhancing the MOSFET performance                         | 29       |  |

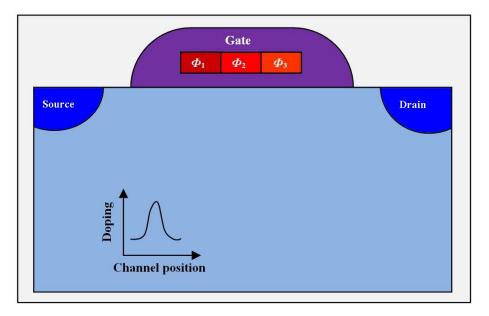

|    |                        | 1.7.1 Channel engineering and gate engineering technologies                      | 30       |  |

|    |                        | 1.7.2 New channel materials and alloys                                           | 30       |  |

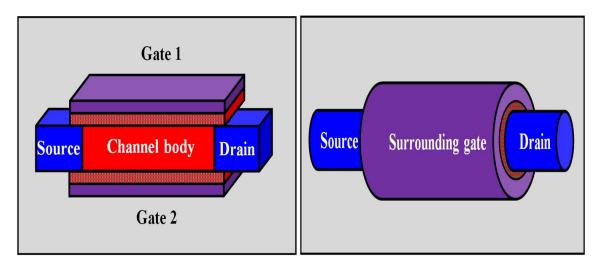

|    |                        | 1.7.3 Multigate MOSFET prototypes                                                | 31       |  |

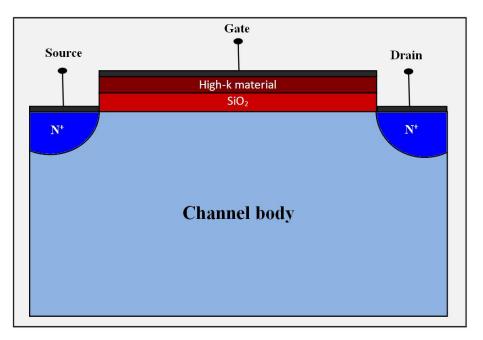

|    |                        | 1.7.4 Dielectric gate development                                                | 32       |  |

|    | 1.8                    | Conclusion                                                                       | 33       |  |

|    | 1.9                    | References                                                                       | 33       |  |

| 2  | An /                   | ANFIS based approach for the subthreshold behavior modeling of nanoscale         |          |  |

|    | DG                     | MOSFETs including interface traps                                                | 37       |  |

|    | 2.1                    | Introduction                                                                     | 39       |  |

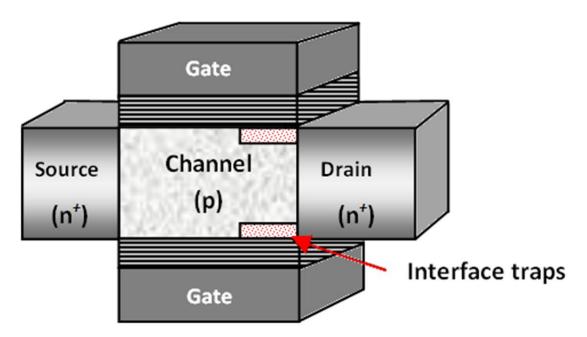

|    | 2.2                    | Parasitic effects and impact on the threshold voltage                            | 41       |  |

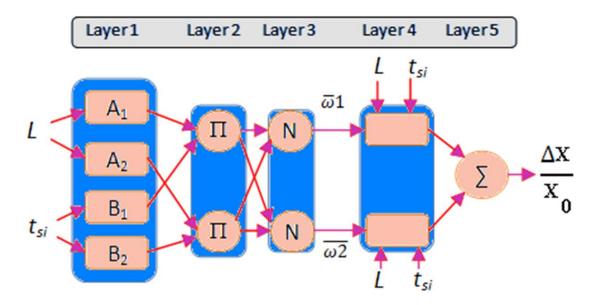

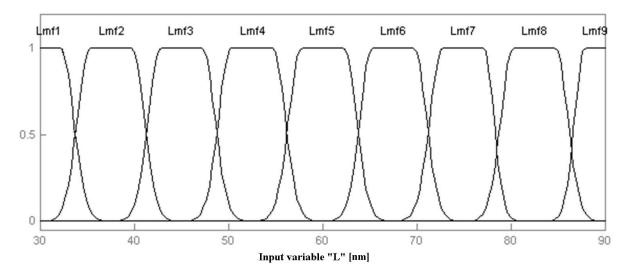

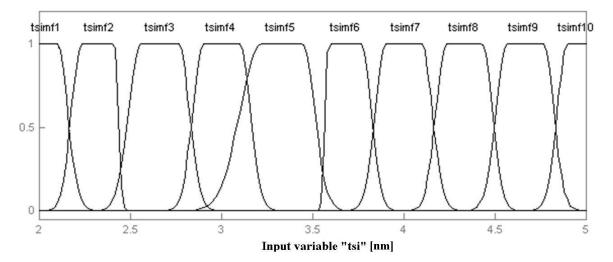

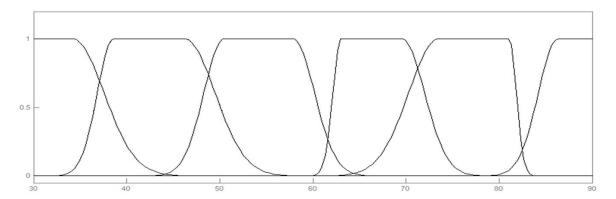

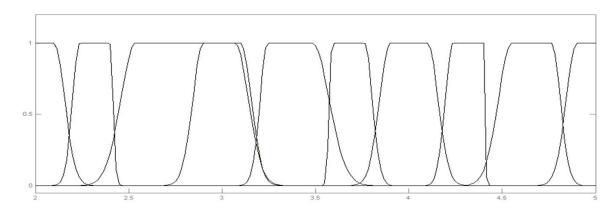

|    | 2.3                    | Background of ANFIS based approach                                               | 44       |  |

|    | 2.4                    | Elaboration of the numerical database                                            | 47       |  |

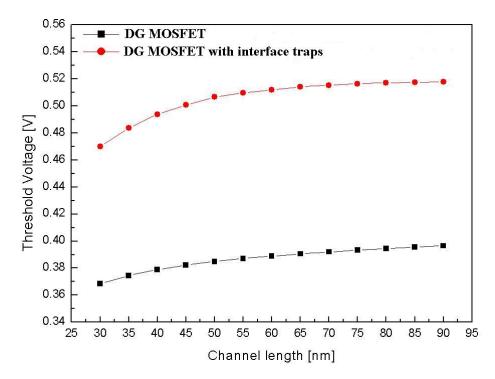

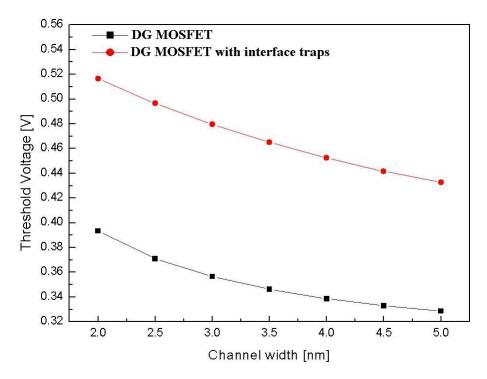

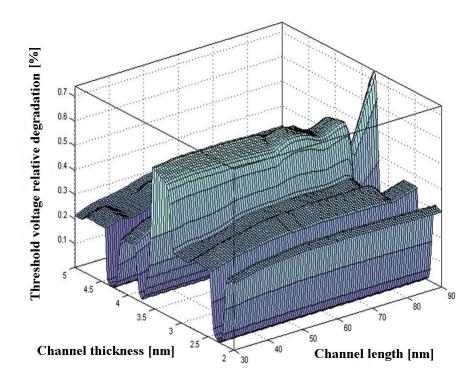

|    | 2.5                    | Results and discussion                                                           | 52       |  |

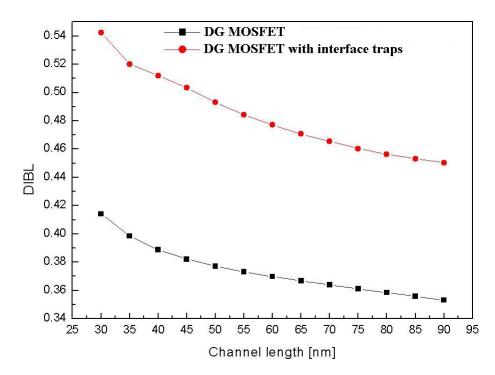

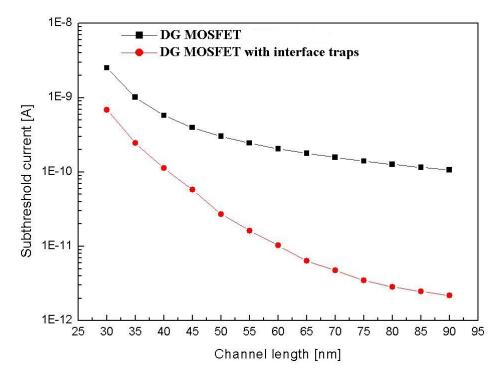

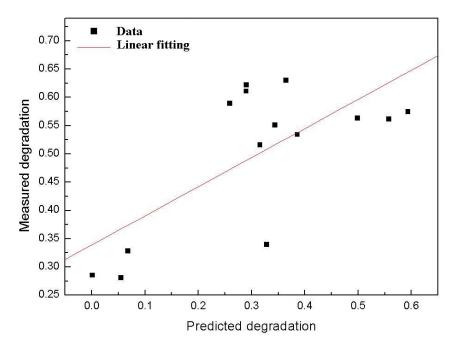

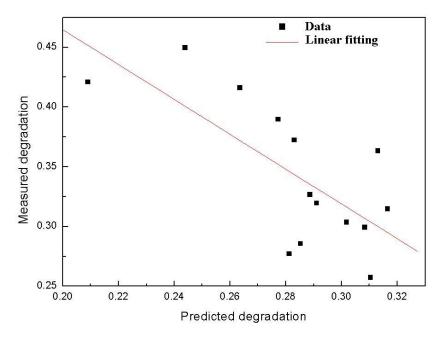

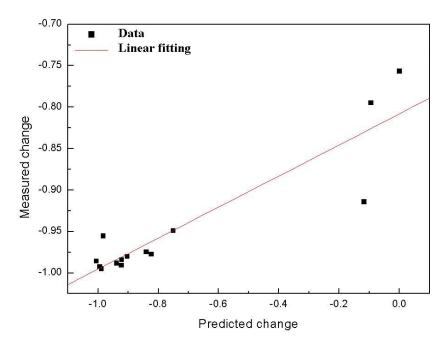

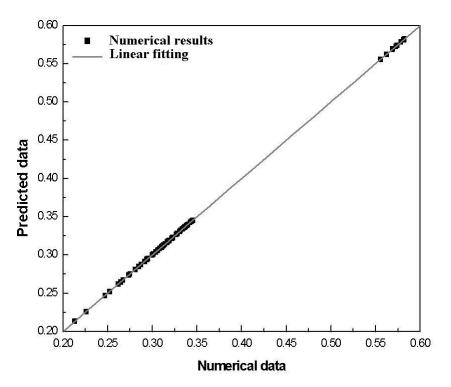

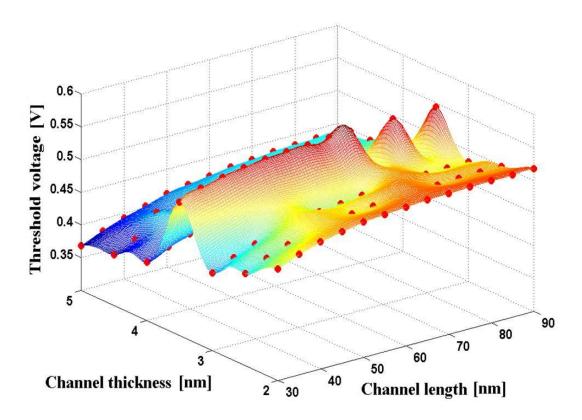

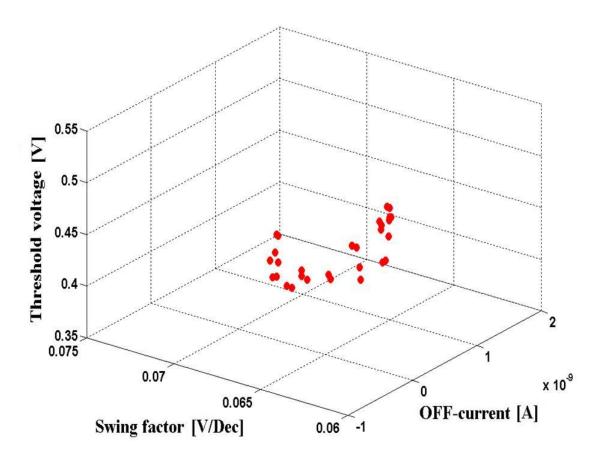

|    |                        | 2.5.1 Global modeling of the subthreshold behavior                               | 52       |  |

|   |                                                                                          | 2.5.2 Modeling of the threshold voltage behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 58                                                                                                           |

|---|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

|   |                                                                                          | 2.5.3 Modeling of the Swing factor behavior                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 61                                                                                                           |

|   | 2.6                                                                                      | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 64                                                                                                           |

|   | 2.7                                                                                      | References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 65                                                                                                           |

| 3 | A su                                                                                     | urrogate based approach for the modeling and design of nanoscale DG MOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -                                                                                                            |

|   |                                                                                          | 's including interface traps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 69                                                                                                           |

|   |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 71                                                                                                           |

|   | 3.2                                                                                      | Classification of various parasitic mechanisms in MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 75                                                                                                           |

|   |                                                                                          | 3.2.1 Short channel effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 75                                                                                                           |

|   |                                                                                          | 3.2.2 Quantum mechanical confinement effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 76                                                                                                           |

|   |                                                                                          | 3.2.3 Hot carrier effects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 77                                                                                                           |

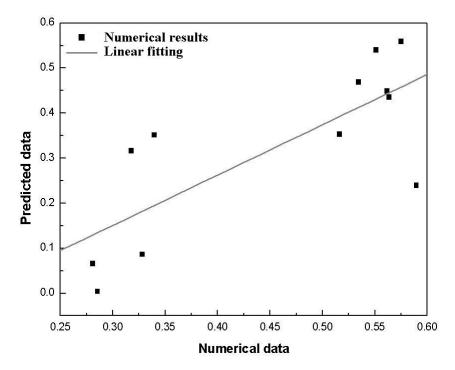

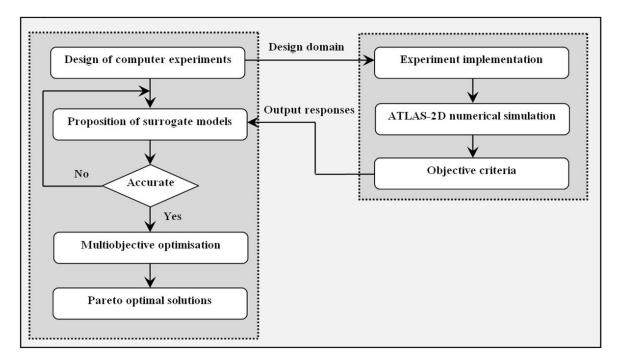

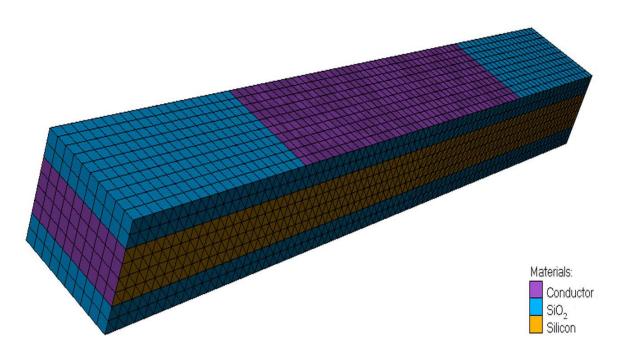

|   | 3.3                                                                                      | Presentation of the proposed modeling framework                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 78                                                                                                           |

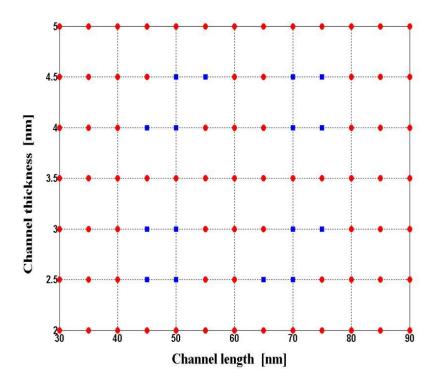

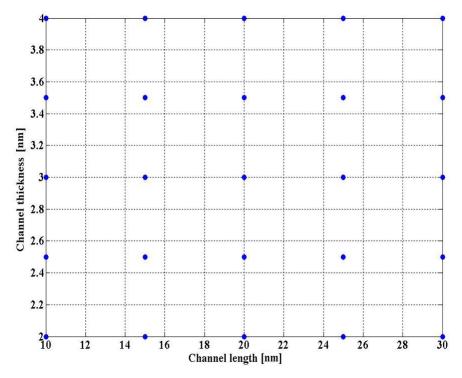

|   |                                                                                          | 3.3.1 Design of computer experiments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 79                                                                                                           |

|   |                                                                                          | 3.3.2 Development of the surrogate models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 80                                                                                                           |

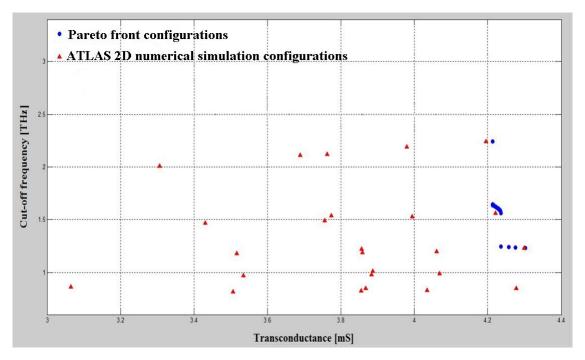

|   | 3.4                                                                                      | 3.3.3 Multi-objective optimization procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 82<br>84                                                                                                     |

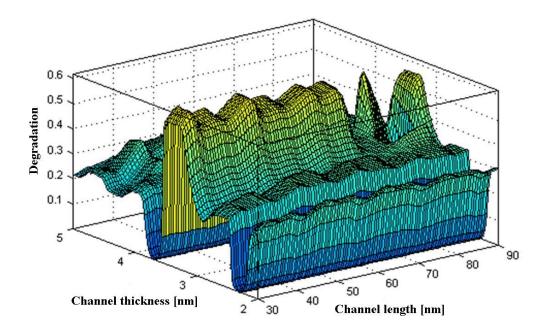

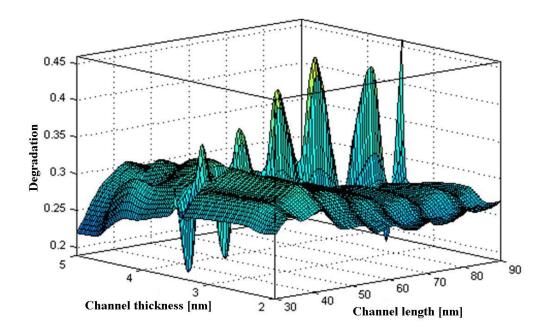

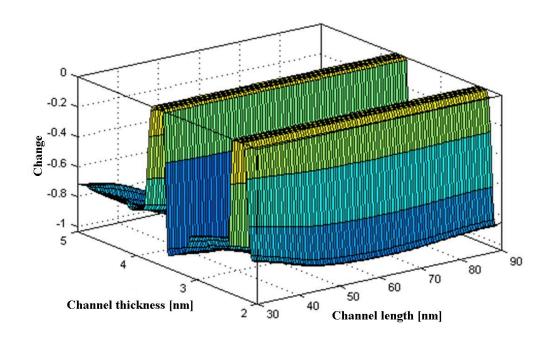

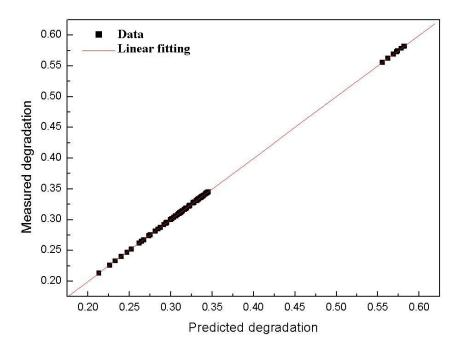

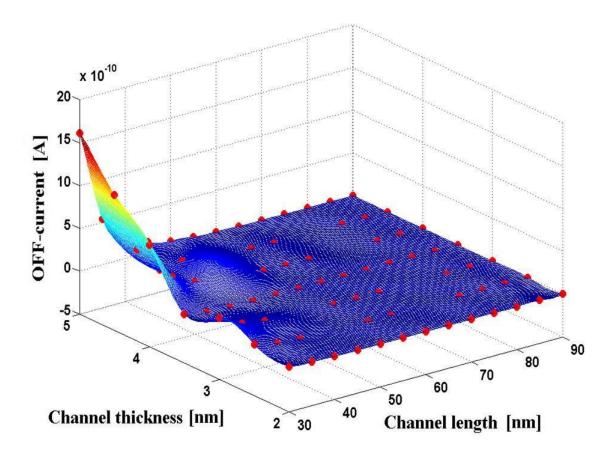

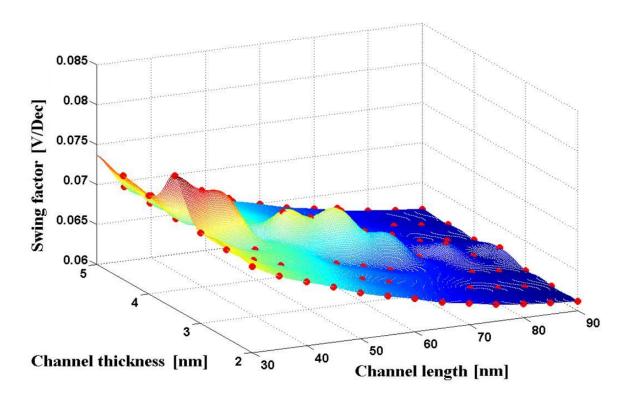

|   | 5.4                                                                                      | 3.4.1 Modeling and optimization of the subthreshold performances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 04<br>84                                                                                                     |

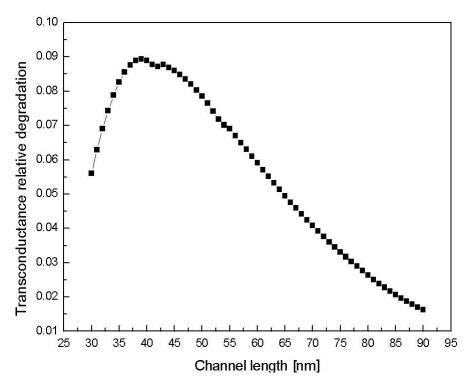

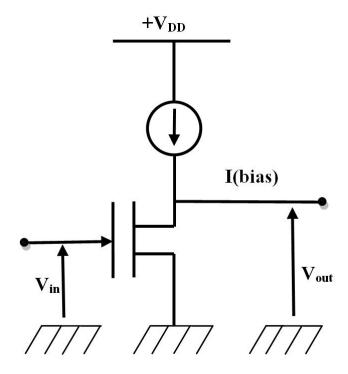

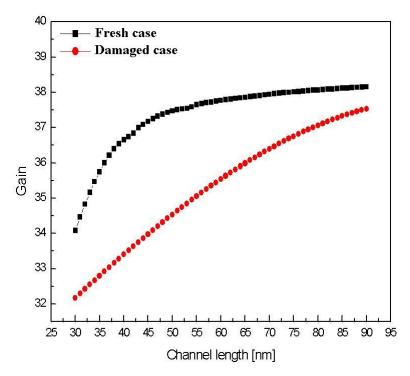

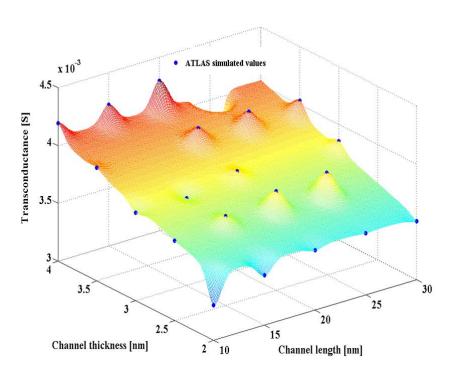

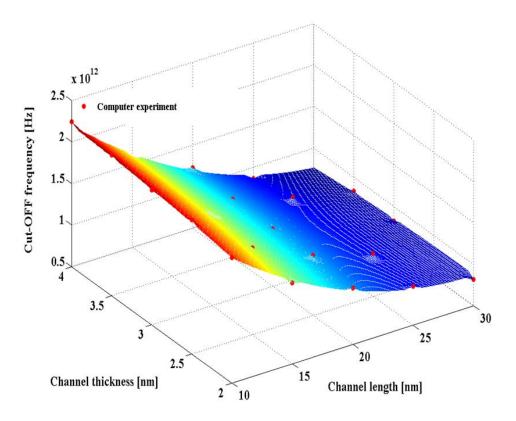

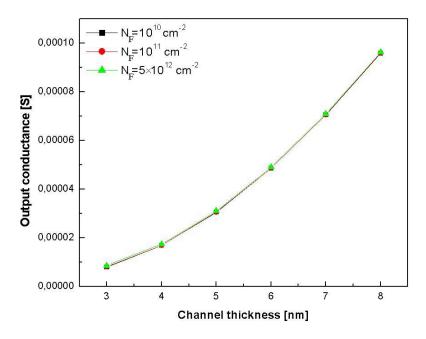

|   |                                                                                          | 3.4.2 Modeling and optimization of the analog/RF performances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 04<br>93                                                                                                     |

|   | 3.5                                                                                      | Conclusion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 98                                                                                                           |

|   | 3.6                                                                                      | References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 99                                                                                                           |

|   |                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                              |

| 4 |                                                                                          | CAD based approach for the performance improvement of nanoscale DC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                              |

|   | MO                                                                                       | SFETs including interface traps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 105                                                                                                          |

|   | 11                                                                                       | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 107                                                                                                          |

|   | 4.1                                                                                      | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 107                                                                                                          |

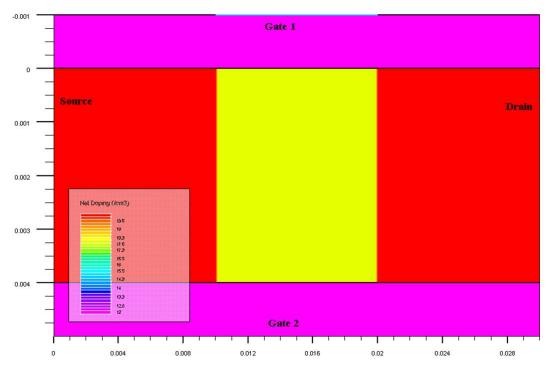

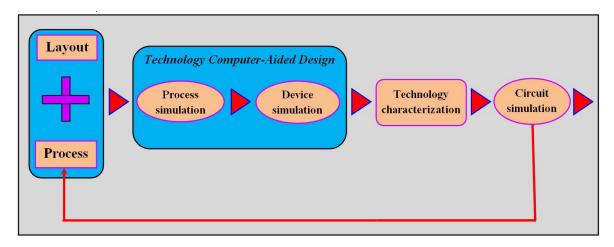

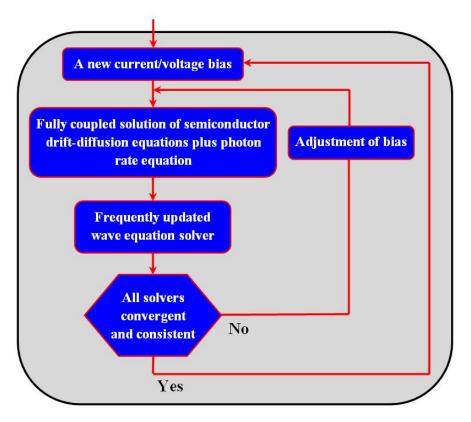

|   | <ul><li>4.1</li><li>4.2</li><li>4.3</li></ul>                                            | Technology Computer-Aided Design simulation for nanoscale design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 107<br>107                                                                                                   |

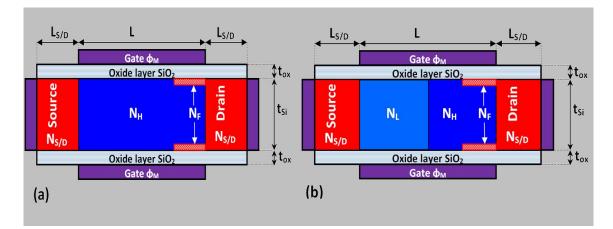

|   | 4.2                                                                                      | Technology Computer-Aided Design simulation for nanoscale design<br>An improved gate engineering based design for nanoscale DG JL MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                              |

|   | 4.2                                                                                      | Technology Computer-Aided Design simulation for nanoscale design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 107                                                                                                          |

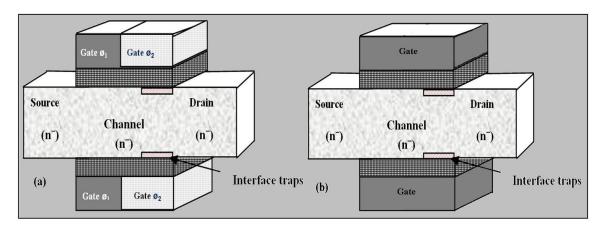

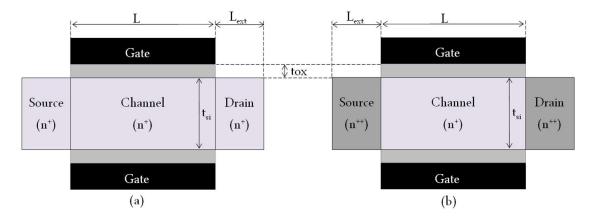

|   | 4.2                                                                                      | Technology Computer-Aided Design simulation for nanoscale design<br>An improved gate engineering based design for nanoscale DG JL MOSFETs<br>including interface traps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 107<br>109                                                                                                   |

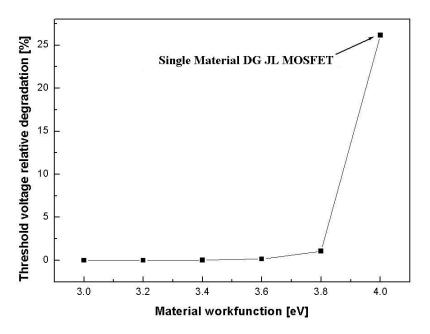

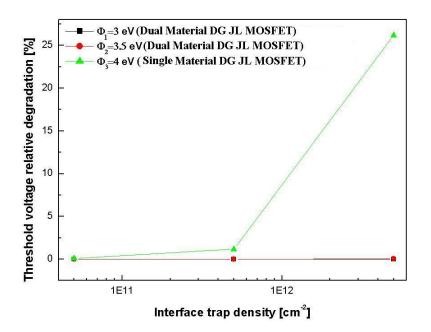

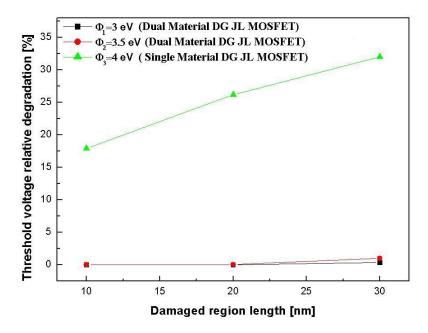

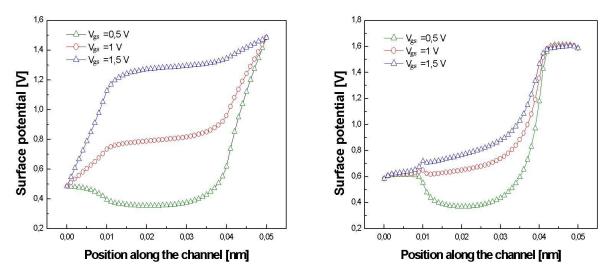

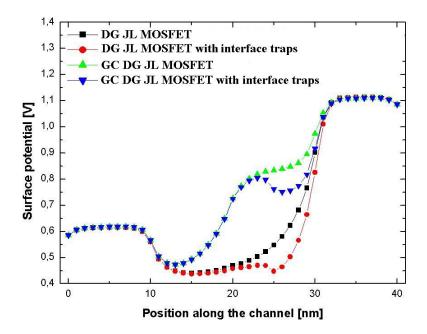

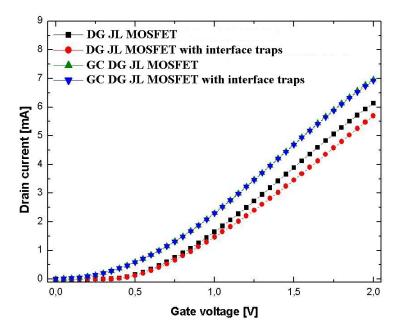

|   | 4.2                                                                                      | Technology Computer-Aided Design simulation for nanoscale designAn improved gate engineering based design for nanoscale DG JL MOSFETsincluding interface traps4.3.1Numerical simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 107<br>109<br>109                                                                                            |

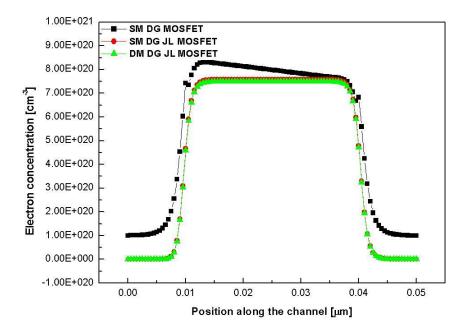

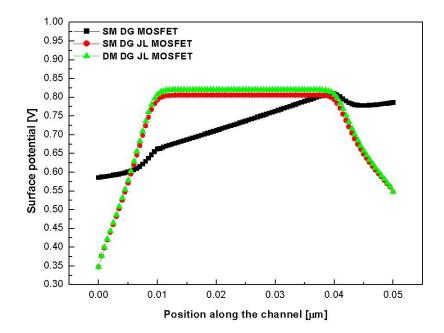

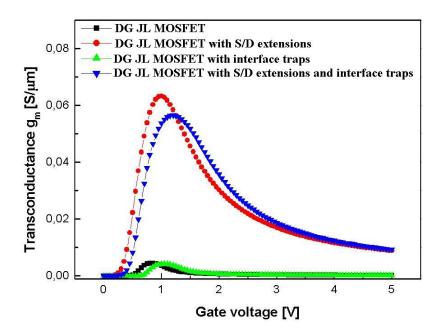

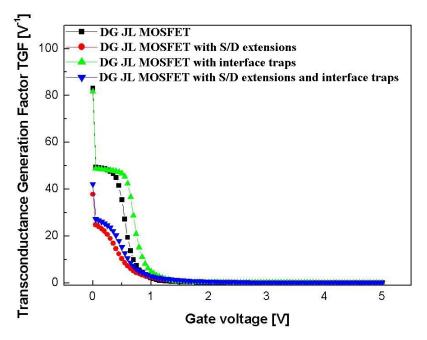

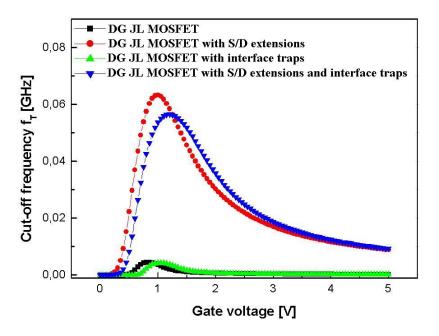

|   | 4.2<br>4.3                                                                               | Technology Computer-Aided Design simulation for nanoscale designAn improved gate engineering based design for nanoscale DG JL MOSFETsincluding interface traps4.3.1Numerical simulations4.3.2Results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 107<br>109<br>109                                                                                            |

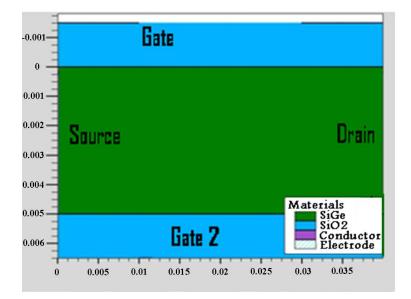

|   | 4.2<br>4.3                                                                               | Technology Computer-Aided Design simulation for nanoscale designAn improved gate engineering based design for nanoscale DG JL MOSFETsincluding interface traps4.3.1Numerical simulations4.3.2Results and discussionAn improved SiGe based design for nanoscale DG MOSFETs including interface trapsface traps4.4.1Numerical simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 107<br>109<br>109<br>110<br>114<br>115                                                                       |

|   | <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul>                                            | Technology Computer-Aided Design simulation for nanoscale designAn improved gate engineering based design for nanoscale DG JL MOSFETsincluding interface traps4.3.1Numerical simulations4.3.2Results and discussionAn improved SiGe based design for nanoscale DG MOSFETs including interface traps4.4.1Numerical simulations4.4.2Results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 107<br>109<br>109<br>110<br>114<br>115                                                                       |

|   | 4.2<br>4.3                                                                               | Technology Computer-Aided Design simulation for nanoscale designAn improved gate engineering based design for nanoscale DG JL MOSFETsincluding interface traps4.3.1Numerical simulations4.3.2Results and discussionAn improved SiGe based design for nanoscale DG MOSFETs including interface traps4.4.1Numerical simulations4.4.2Results and discussionAn improved source/drain extensions based design for nanoscale DG JL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 107<br>109<br>109<br>110<br>114<br>115<br>116                                                                |

|   | <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul>                                            | Technology Computer-Aided Design simulation for nanoscale designAn improved gate engineering based design for nanoscale DG JL MOSFETsincluding interface traps4.3.1Numerical simulations4.3.2Results and discussionAn improved SiGe based design for nanoscale DG MOSFETs including interface traps4.4.1Numerical simulations4.4.2Results and discussionAn improved sign for nanoscale DG MOSFETs including interface trapsA.1Numerical simulationsA.2Results and discussionA.3An improved source/drain extensions based design for nanoscale DG JLMOSFETs including interface traps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 107<br>109<br>109<br>110<br>114<br>115<br>116<br>119                                                         |

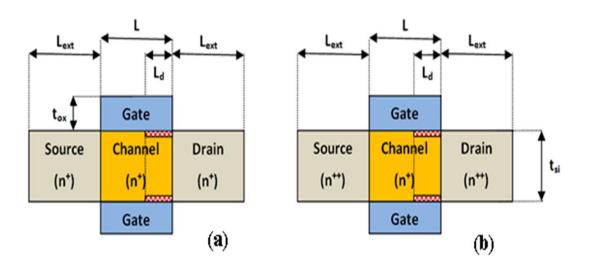

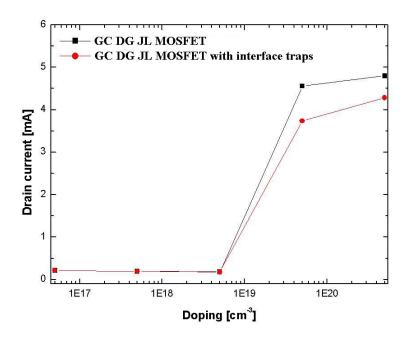

|   | <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul>                                            | Technology Computer-Aided Design simulation for nanoscale designAn improved gate engineering based design for nanoscale DG JL MOSFETsincluding interface traps4.3.1Numerical simulations4.3.2Results and discussionAn improved SiGe based design for nanoscale DG MOSFETs including interface traps4.4.1Numerical simulations4.4.2Results and discussionAn improved source/drain extensions based design for nanoscale DG JLMOSFETs including interface traps4.5.1Numerical simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 107<br>109<br>109<br>110<br>114<br>115<br>116<br>119<br>120                                                  |

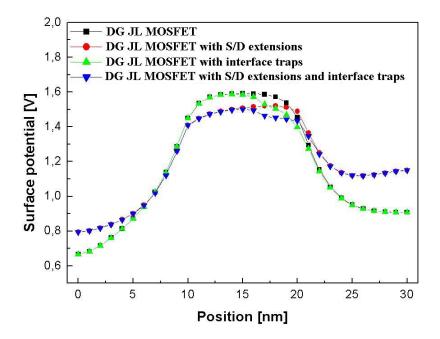

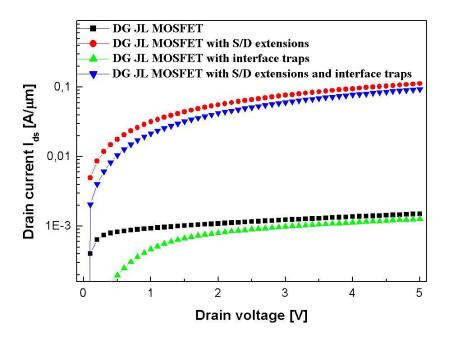

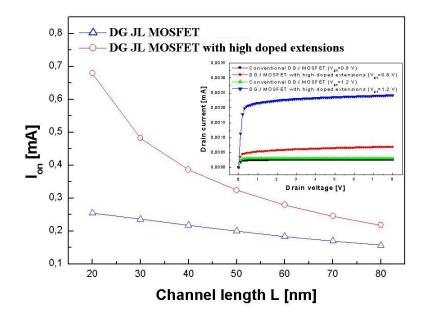

|   | <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>                           | Technology Computer-Aided Design simulation for nanoscale designAn improved gate engineering based design for nanoscale DG JL MOSFETsincluding interface traps4.3.1Numerical simulations4.3.2Results and discussionAn improved SiGe based design for nanoscale DG MOSFETs including interface trapsface traps4.4.1Numerical simulations4.4.2Results and discussionAn improved source/drain extensions based design for nanoscale DG JLMOSFETs including interface traps4.5.1Numerical simulations4.5.2Results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 107<br>109<br>109<br>110<br>114<br>115<br>116<br>119                                                         |

|   | <ul><li>4.2</li><li>4.3</li><li>4.4</li></ul>                                            | Technology Computer-Aided Design simulation for nanoscale designAn improved gate engineering based design for nanoscale DG JL MOSFETsincluding interface traps4.3.1Numerical simulations4.3.2Results and discussionAn improved SiGe based design for nanoscale DG MOSFETs including interface traps4.4.1Numerical simulations4.4.2Results and discussionAn improved source/drain extensions based design for nanoscale DG JLMOSFETs including interface traps4.5.1Numerical simulations4.5.2Results and discussion4.5.2Results and discussionAn improved source/drain extensions based design for nanoscale DG JLMOSFETs including interface traps4.5.1Numerical simulations4.5.2Results and discussion4.5.2Results and discussionAn improved of the source/drain extensions on the nanoscale DG JL MOSFETs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 107<br>109<br>109<br>110<br>114<br>115<br>116<br>119<br>120<br>121                                           |

|   | <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>                           | Technology Computer-Aided Design simulation for nanoscale designAn improved gate engineering based design for nanoscale DG JL MOSFETsincluding interface traps4.3.1 Numerical simulations4.3.2 Results and discussionAn improved SiGe based design for nanoscale DG MOSFETs including interface traps4.4.1 Numerical simulations4.4.2 Results and discussion4.4.2 Results and discussionAn improved source/drain extensions based design for nanoscale DG JLMOSFETs including interface traps4.5.1 Numerical simulations4.5.2 Results and discussion4.5.2 Results and discussion4.5.2 Results and discussion4.5.3 Inductions4.5.4 Results and discussion4.5.5 Including interface traps4.5.6 Inductions4.5.7 Results and discussion4.5.8 Results and discussion4.5.9 Results and discussion4.5.1 Numerical simulations4.5.2 Results and discussion4.5.3 Results and discussion4.5.4 Results and discussion4.5.5 Results and discussion4.5.6 Results and discussion4.5.7 Results and discussion4.5.8 Results and discussion4.5.9 Results and discussion4.5.1 Results and discussion4.5.2 Results and discussion4.5.3 Results and discussion4.5.4 Results and discussion4.5.5 Results and discussion <t< td=""><td>107<br/>109<br/>109<br/>110<br/>114<br/>115<br/>116<br/>119<br/>120<br/>121<br/>126</td></t<> | 107<br>109<br>109<br>110<br>114<br>115<br>116<br>119<br>120<br>121<br>126                                    |

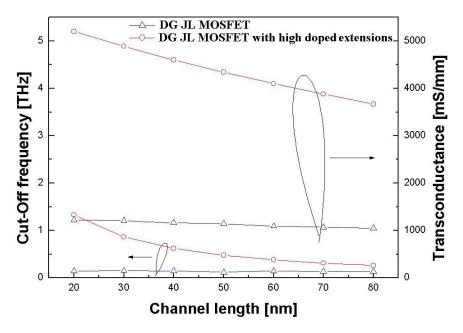

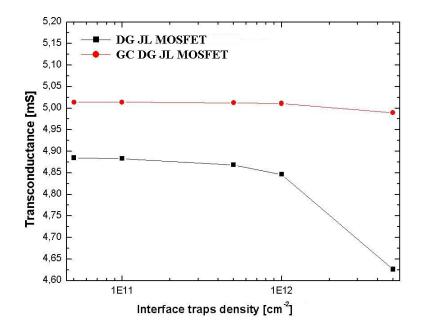

|   | <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>                           | Technology Computer-Aided Design simulation for nanoscale designAn improved gate engineering based design for nanoscale DG JL MOSFETsincluding interface traps4.3.1Numerical simulations4.3.2Results and discussionAn improved SiGe based design for nanoscale DG MOSFETs including interface trapsface traps4.4.1Numerical simulations4.4.2Results and discussion4.4.3Results and discussionAn improved source/drain extensions based design for nanoscale DG JLMOSFETs including interface traps4.5.1Numerical simulations4.5.2Results and discussionImpact of the source/drain extensions on the nanoscale DG JL MOSFETsincluding interface traps in terms of analog/RF criteria4.6.1Numerical simulations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 107<br>109<br>109<br>110<br>114<br>115<br>116<br>119<br>120<br>121<br>126<br>126                             |

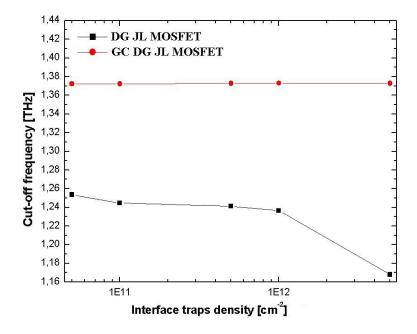

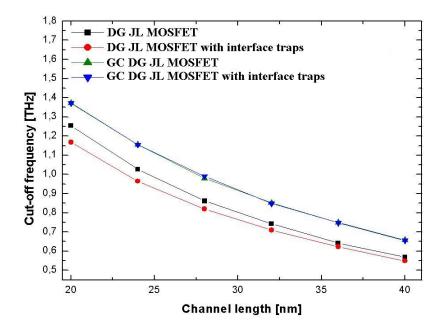

|   | <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>              | Technology Computer-Aided Design simulation for nanoscale designAn improved gate engineering based design for nanoscale DG JL MOSFETsincluding interface traps4.3.1Numerical simulations4.3.2Results and discussionAn improved SiGe based design for nanoscale DG MOSFETs including interface trapsAn improved SiGe based design for nanoscale DG MOSFETs including interface traps4.4.1Numerical simulations4.4.2Results and discussionAn improved source/drain extensions based design for nanoscale DG JLMOSFETs including interface traps4.5.1Numerical simulations4.5.2Results and discussionImpact of the source/drain extensions on the nanoscale DG JL MOSFETsincluding interface traps in terms of analog/RF criteria4.6.1Numerical simulations4.6.2Results and discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 107<br>109<br>109<br>110<br>114<br>115<br>116<br>119<br>120<br>121<br>126                                    |

|   | <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> </ul>                           | Technology Computer-Aided Design simulation for nanoscale designAn improved gate engineering based design for nanoscale DG JL MOSFETsincluding interface traps4.3.1Numerical simulations4.3.2Results and discussionAn improved SiGe based design for nanoscale DG MOSFETs including interface traps4.4.1Numerical simulations4.4.2Results and discussion4.4.2Results and discussionAn improved source/drain extensions based design for nanoscale DG JLMOSFETs including interface traps4.5.1Numerical simulations4.5.2Results and discussion4.5.3Results and discussion4.5.4Numerical simulations4.5.5Numerical simulations4.5.6Results and discussion4.5.7Results and discussionAn improved of the source/drain extensions on the nanoscale DG JL MOSFETsincluding interface traps in terms of analog/RF criteria4.6.1Numerical simulations4.6.2Results and discussionAn improved graded channel doping based design for nanoscale DG JL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 107<br>109<br>109<br>110<br>114<br>115<br>116<br>119<br>120<br>121<br>126<br>126<br>128                      |

|   | <ul> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>4.5</li> <li>4.6</li> </ul>              | Technology Computer-Aided Design simulation for nanoscale design An improved gate engineering based design for nanoscale DG JL MOSFETs including interface traps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 107<br>109<br>109<br>110<br>114<br>115<br>116<br>119<br>120<br>121<br>126<br>126<br>128<br>131               |